| 1a) |  |

1b) |  |

1c) |  |

1d) |  |

1e) |  |

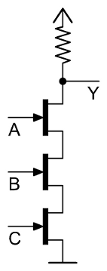

| Inverter with 1a) resistor, 1b) enhancement mode and 1c) depletion mode pull-up 1d) super inverter 1e) super buffer | |||||||||

| 2a) |  |

2b) |  |

2c) |  |

2d) |  |

2e) |  |

| 2a) 2-input NOR 2b) compact version of the previous 2c) 3-input NOR 1d) 2-input super NOR 2f) 2-input OR | |||||||||

| 3a) |  |

3b) |  |

3c) |  |

3d) |  |

3e) |  |

3f) |  |

| 4a) 2-input NAND 4b) 3-input NAND 4c) 2-input super NAND 4d) 2-input AND 4e) two 2-input NANDs with one common input - transistors and 4f) gates | |||||||||||

| 4a) |  |

4b) |  |

4c) |  |

4d) |  |

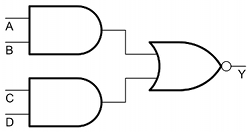

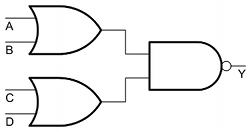

| 4a) 2-2 AND-OR-INVERT (AOI22) - transistors and 4b) gates, 4c) 2-2 OR-AND-INVERT (OAI22) - transistors and 4d) gates | |||||||

| 5a) |  |

| 5a) 2-input XOR using inputs as pull-down | |

| 5b) |  |

5c) |  |

5d) |  |

5e) |  |

| 5b) 2-input XOR - transistors and 5c) gates, 5d) 2-input XOR using AOI22 - transistors and 5e) gates | |||||||

| 5f) |  |

5g) |  |

5h) |  |

5i) |  |

| 5f) 2-input XNOR - transistors and 5g) gates, 5h) 2-input XNOR using AOI22 - transistors and 5i) gates | |||||||

| 6a) |  |

| 6a) Inverting Schmitt Trigger | |